India plans to cap the commissions app-based taxi aggregators such as Uber Technologies Inc and home-grown Ola earn on rides to a maximum 10 percent of the total fare, according to a draft proposal seen by Reuters, a move industry experts warned would hit revenue and operations.

Such a law would be another blow to San Francisco-based Uber after the ride-hailing firm was stripped of its license to carry paying passengers in London on Monday for the second time in just more than two years over a “pattern of failures” on safety and security.

The Indian government has proposed reducing the commission from the about 20 percent of the total fair charged at present, the 23-page document titled Central Guidelines for Aggregators says.

Photo: Reuters

The government has also proposed stricter safety checks for drivers and wants to cap their working hours at 12 per day, amid fears long shifts are putting passenger safety at risk.

The Indian Ministry of Road Transport and Highways did not respond to a request for comment outside working hours. Uber and Ola also did not respond.

The proposal could still change, but industry experts say it could halve Uber and Softbank-backed Ola’s revenues from rides.

India accounts for an estimated 11 percent of Uber’s global rides annually.

“The 10 percent [commission] is not viable, it has to be something around 20 percent,” former Ola corporate president of new initiatives Joy Bandekar said, adding that the system could not survive at the lower rate.

India is a key growth market for ride-hailing companies as people seek to avoid driving themselves on its congested roads.

To boost safety, the proposal says taxi companies should set up a control room that can track vehicles and conduct a facial recognition check of drivers every three hours.

The companies should also provide insurance for drivers and riders, and store all the data collected on the app on a local server for two years, it says.

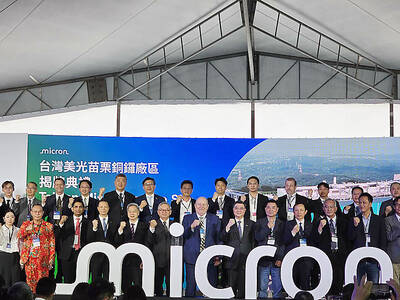

UNPRECEDENTED PACE: Micron Technology has announced plans to expand manufacturing capabilities with the acquisition of a new chip plant in Miaoli Micron Technology Inc unveiled a newly acquired chip plant in Miaoli County yesterday, as the company expands capacity to meet growing demand for advanced DRAM chips, including high-bandwidth memory chips amid the artificial intelligence boom. The plant in Miaoli County’s Tongluo Township (銅鑼), which Micron acquired from Powerchip Semiconductor Manufacturing Corp (力積電) for US$1.8 billion, is expected to make a sizeable capacity contribution to the company from fiscal 2028, the company said in a statement. It would be an extended production site of Micron’s large-scale manufacturing hub in Taichung, the company said. As the global semiconductor industry is racing to reach US$1 trillion

Singapore-based ride-hailing and delivery giant Grab Holdings Ltd has applied for regulatory approval to acquire the Taiwan operations of Germany-based Delivery Hero SE's Foodpanda in a deal valued at about US$600 million. Grab submitted the filing to the Fair Trade Commission on Friday last week, with the transaction subject to regulatory review and approval, the company said in a statement yesterday. Its independent governance structure would help foster a healthy and competitive market in Taiwan if the deal is approved, Grab said. Grab, which is listed on the NASDAQ, said in the filing that US-based Uber Technologies Inc holds about 13 percent of

ABOVE LEGAL REQUIREMENT: The Ministry of Economic Affairs is prepared if LNG supply is disrupted, with more than the legal requirement of 11 days of inventory Taiwan has largely secured liquefied natural gas (LNG) supplies through May and arranged about half of June’s supply, Minister of Economic Affairs Kung Ming-hsin (龔明鑫) said yesterday. Since the Middle East conflict began on Feb. 28, Taiwan’s LNG inventories have remained more than 12 days, exceeding the legal requirement of 11 days, indicating no major supply concerns for domestic gas and electricity, Kung said at a meeting of the legislature’s Economics Committee in Taipei. The ministry aims to increase the figure to 14 days by the end of next year, he said. While one or two LNG or crude oil shipments for May

Taiwan’s food delivery market could undergo a major shift if Singapore-based Grab Holdings Ltd completes its planned acquisition of Delivery Hero SE’s Foodpanda business in Taiwan, industry experts said. Grab on Monday last week announced it would acquire Foodpanda’s Taiwan operations for US$600 million. The deal is expected to be finalized in the second half of this year, with Grab aiming to complete user migration to its platform by the first half of next year. A duopoly between Uber Eats and Foodpanda dominates Taiwan’s delivery market, a structure that has remained intact since the Fair Trade Commission (FTC) blocked Uber Technologies Inc’s